GD25Q64C

# GD25Q64C

# DATASHEET

TLE:0755-88821663 88837366 深圳市福田区深南大道电子科技大厦C座23E www.yxd163.com

# Contents

| 1. | FE                      | ATURES                                                                               | 4  |

|----|-------------------------|--------------------------------------------------------------------------------------|----|

| 2. | GE                      | NERAL DESCRIPTION                                                                    | 5  |

| 3. | MF                      | MORY ORGANIZATION                                                                    | 7  |

|    |                         |                                                                                      |    |

| 4. | DE                      | VICE OPERATION                                                                       | 8  |

| 5. | DA                      | TA PROTECTION                                                                        | 9  |

| 6. | ST                      | ATUS REGISTER                                                                        | 11 |

| 7. | со                      | OMMANDS DESCRIPTION                                                                  | 13 |

| 7  | .1.                     | WRITE ENABLE (WREN) (06H)                                                            | 16 |

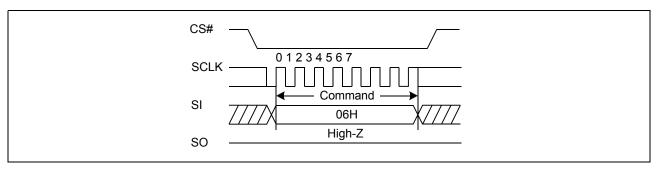

|    | .1.                     | WRITE DISABLE (WRDI) (0011)<br>Write Disable (WRDI) (04H)                            |    |

|    | .2.                     | WRITE ENABLE (WROF) (0411)                                                           |    |

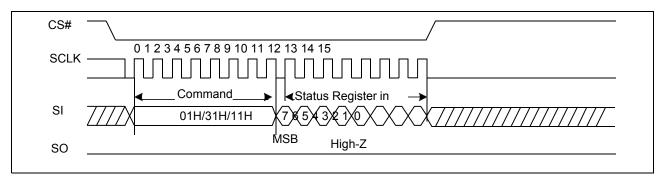

|    | . <i>3</i> .<br>.4.     | READ STATUS REGISTER (RDSR) (05H OR 35H OR 15H)                                      |    |

|    | . <del>.</del> .<br>.5. | WRITE STATUS REGISTER (WRSR) (01H OR 31H OR 11H)                                     |    |

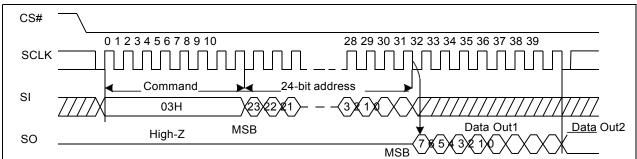

|    | . <i>5</i> .<br>.6.     | READ DATA BYTES (READ) (03H)                                                         |    |

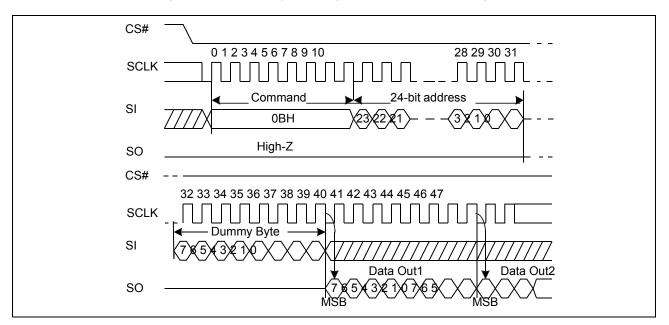

|    | .0.                     | READ DATA BYTES (READ) (0511)<br>READ DATA BYTES AT HIGHER SPEED (FAST READ) (0BH)   |    |

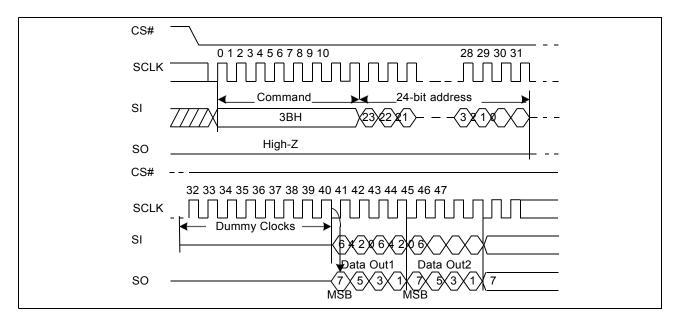

|    | . <i>7</i> .<br>.8.     | DUAL OUTPUT FAST READ (3BH)                                                          |    |

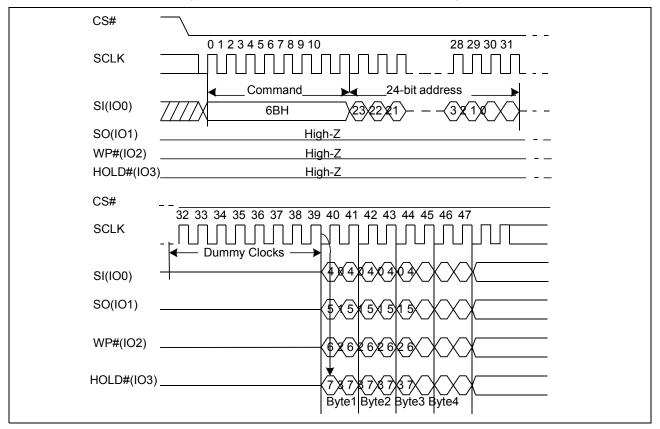

|    | .0.<br>.9.              | QUAD OUTPUT FAST READ (6BH)                                                          |    |

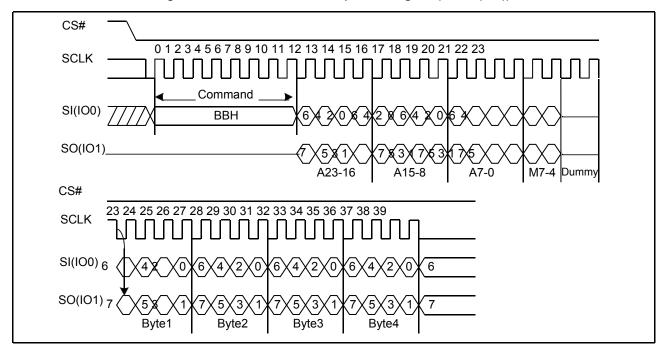

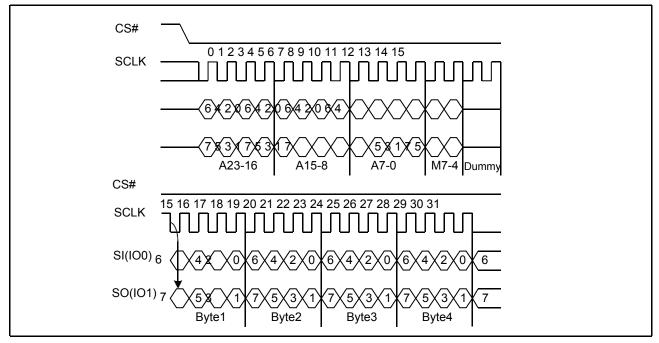

|    | .10.                    | DUAL I/O FAST READ (BBH)                                                             |    |

|    | .11.                    | QUAD I/O FAST READ (EBH)                                                             |    |

|    | .12.                    | QUAD I/O WORD FAST READ (E7H)                                                        |    |

|    | .13.                    | SET BURST WITH WRAP (77H)                                                            |    |

|    | .14.                    | PAGE PROGRAM (PP) (02H)                                                              |    |

|    | .15.                    | QUAD PAGE PROGRAM (32H)                                                              |    |

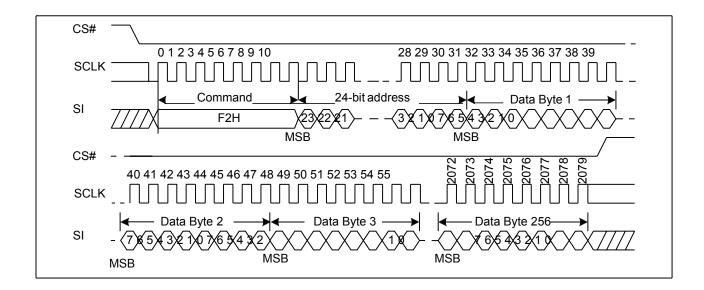

|    | .16.                    | FAST PAGE PROGRAM (FPP) (F2H)                                                        |    |

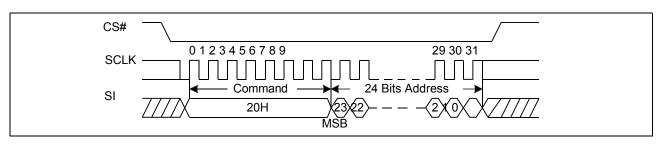

|    | .17.                    | SECTOR ERASE (SE) (20H)                                                              |    |

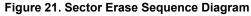

|    | .18.                    | 32KB BLOCK ERASE (BE) (52H)                                                          |    |

|    | .19.                    | 64KB BLOCK ERASE (BE) (D8H)                                                          |    |

|    | .20.                    | CHIP ERASE (CE) (60/C7H)                                                             |    |

|    | .21.                    | DEEP POWER-DOWN (DP) (B9H)                                                           |    |

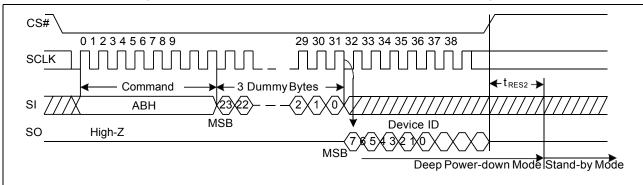

|    | .22.                    | RELEASE FROM DEEP POWER-DOWN OR HIGH PERFORMANCE MODE AND READ DEVICE ID (RDI) (ABH) |    |

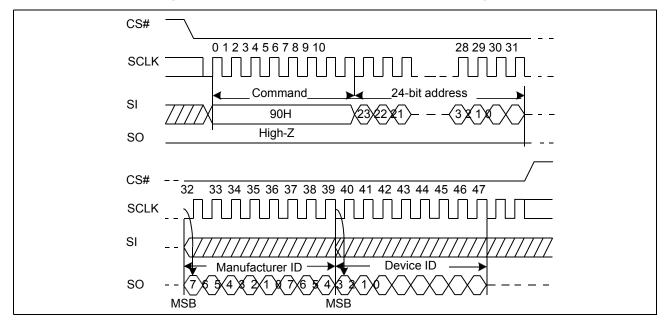

|    | .23.                    | READ MANUFACTURE ID/ DEVICE ID (REMS) (90H)                                          |    |

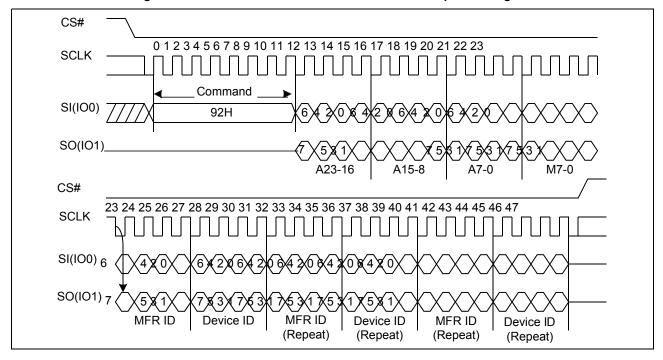

| 7  | .24.                    | DUAL I/O READ MANUFACTURE ID/ DEVICE ID (92H)                                        |    |

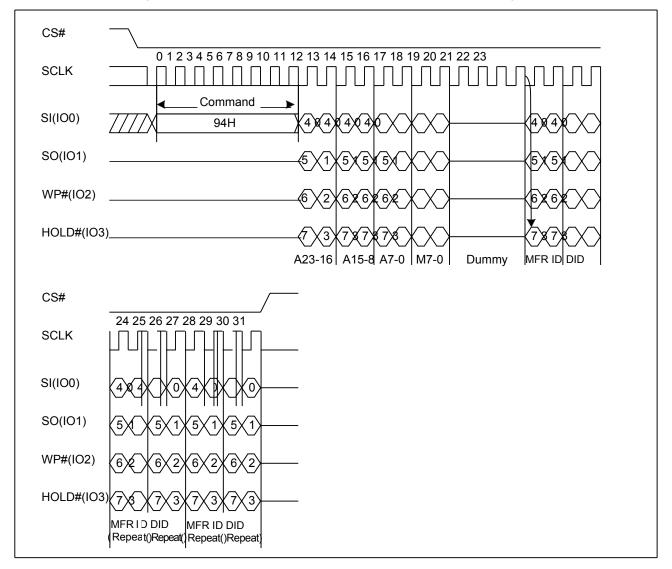

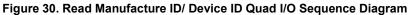

| 7  | .25.                    | QUAD I/O READ MANUFACTURE ID/ DEVICE ID (94H)                                        |    |

| 7  | .26.                    | READ IDENTIFICATION (RDID) (9FH)                                                     |    |

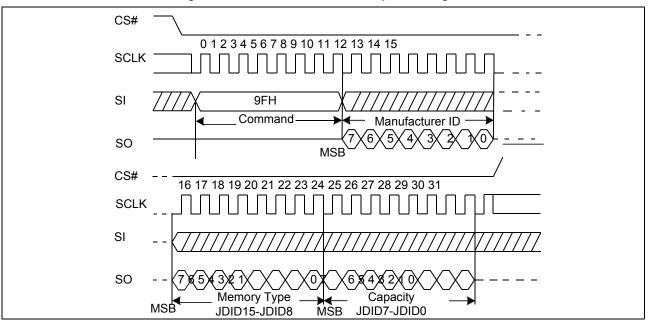

| 7  | .27.                    | HIGH PERFORMANCE MODE (HPM) (A3H)                                                    |    |

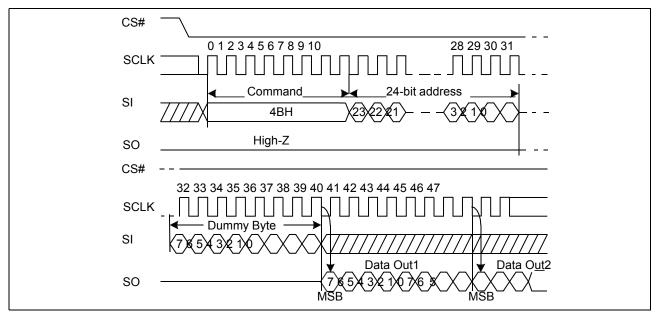

| 7  | .28.                    | READ UNIQUE ID (4BH)                                                                 | 40 |

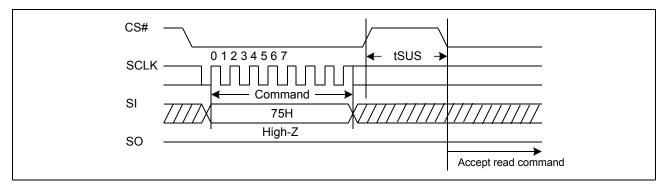

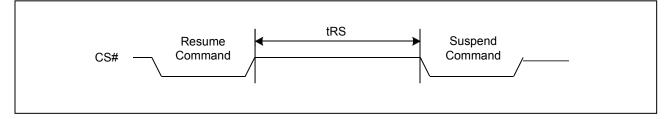

| 7  | .29.                    | PROGRAM/ERASE SUSPEND (PES) (75H)                                                    | 41 |

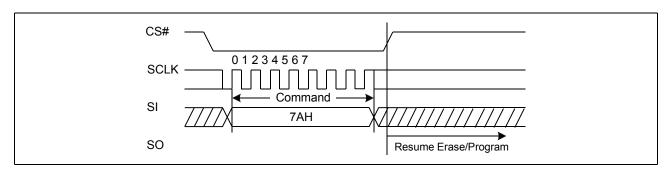

| 7  | .30.                    | PROGRAM/ERASE RESUME (PER) (7AH)                                                     | 42 |

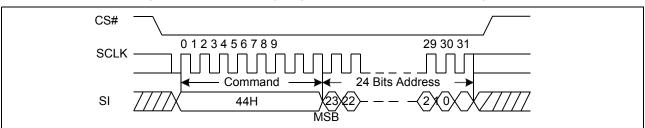

| 7  | .31.                    | Erase Security Registers (44H)                                                       | 42 |

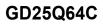

| 7  | .32.                    | PROGRAM SECURITY REGISTERS (42H)                                                     | 43 |

| Ý     | 3.3V Uniform Sector<br><sup>宇翔达</sup> Dual and Quad Serial Flash | GD25Q64C |

|-------|------------------------------------------------------------------|----------|

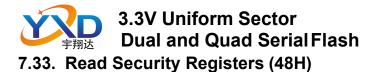

| 7.33. |                                                                  | -        |

| 7.34. | ENABLE RESET (66H) AND RESET (99H)                               |          |

| 7.35. | . READ SERIAL FLASH DISCOVERABLE PARAMETER (5AH)                 |          |

| 8. El | LECTRICAL CHARACTERISTICS                                        | 50       |

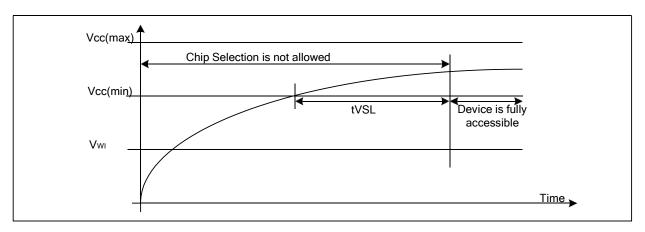

| 8.1.  | POWER-ON TIMING                                                  |          |

| 8.2.  | INITIAL DELIVERY STATE                                           |          |

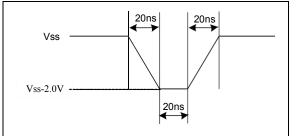

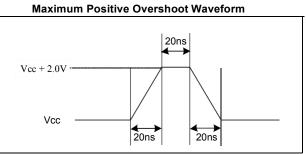

| 8.3.  | ABSOLUTE MAXIMUM RATINGS                                         |          |

| 8.4.  | CAPACITANCE MEASUREMENT CONDITIONS                               |          |

| 8.5.  | DC CHARACTERISTICS                                               |          |

| 8.6.  | AC CHARACTERISTICS                                               |          |

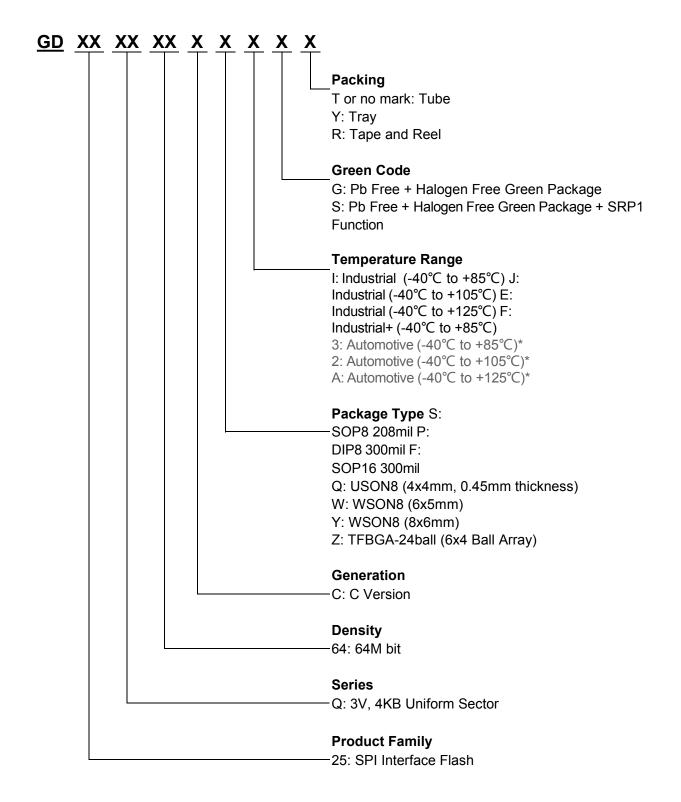

| 9. O  | RDERING INFORMATION                                              |          |

| 9.1.  | VALID PART NUMBERS                                               |          |

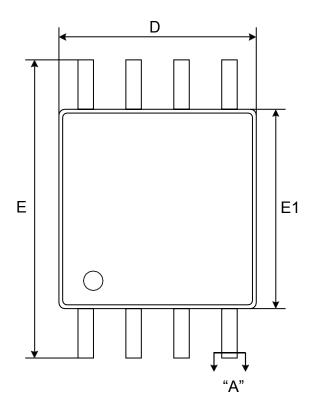

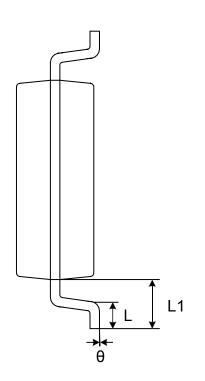

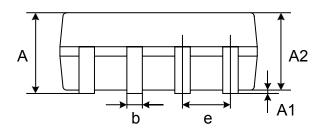

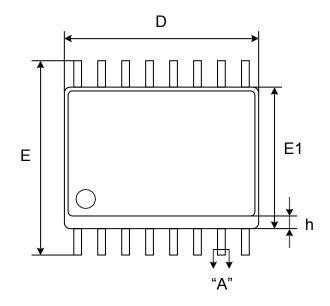

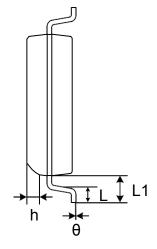

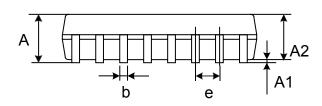

| 10.   | PACKAGE INFORMATION                                              |          |

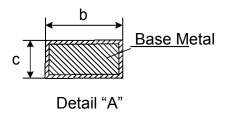

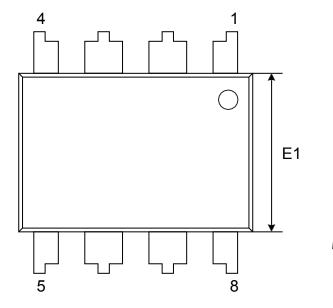

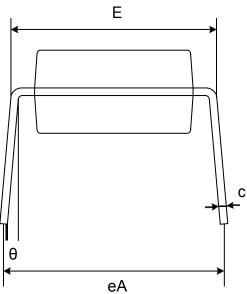

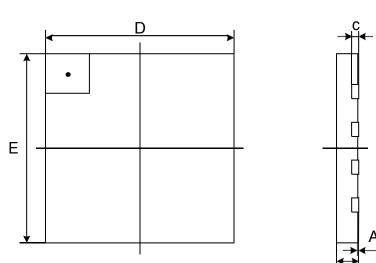

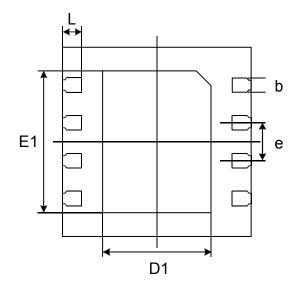

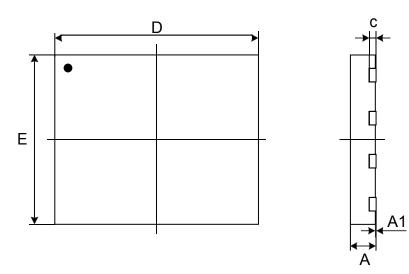

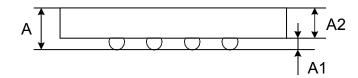

| 10.1. | . PACKAGE SOP8 208MIL                                            |          |

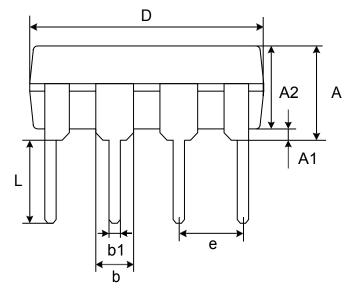

| 10.2. | . PACKAGE DIP8 300MIL                                            |          |

| 10.3. | . PACKAGE SOP16 300MIL                                           |          |

| 10.4. | . PACKAGE USON8 (4*4MM, 0.45MM THICKNESS)                        |          |

| 10.5. | . PACKAGE WSON8 (6*5MM)                                          |          |

| 10.6. | . PACKAGE WSON8 (8*6MM)                                          |          |

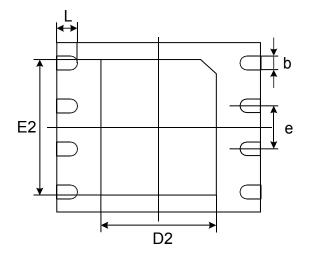

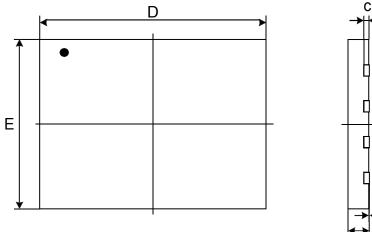

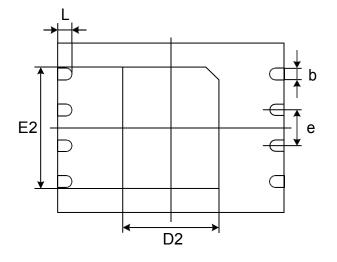

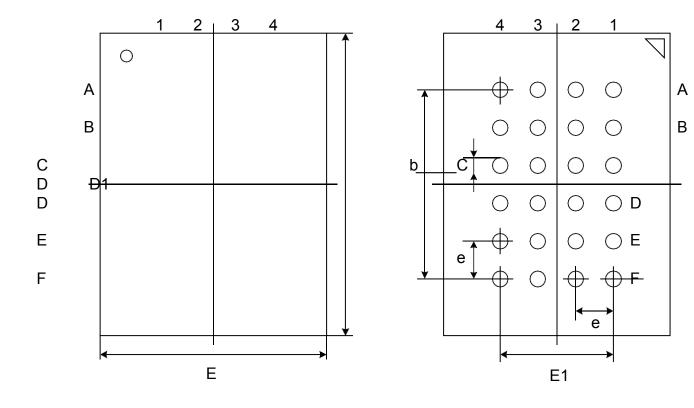

| 10.7. | . PACKAGE TFBGA-24BALL (6*4 BALL ARRAY)                          |          |

| 11.   | REVISION HISTORY                                                 |          |

# GD25Q64C

## 1. FEATURES

- 64M-bit Serial Flash

-8192K-byte

-256 bytes per programmable page

- Standard, Dual, Quad SPI

Standard SPI: SCLK, CS#, SI, SO, WP#, HOLD#

Dual SPI: SCLK, CS#, IO0, IO1, WP#, HOLD#

Quad SPI: SCLK, CS#, IO0, IO1, IO2, IO3

- High Speed Clock Frequency

-120MHz for fast read with 30PF load

-Dual I/O Data transfer up to 240Mbits/s

-Quad I/O Data transfer up to 480Mbits/s

-Continuous Read With 8/16/32/64-byte Wrap

- Software/Hardware Write Protection

Write protect all/portion of memory via software

Enable/Disable protection with WP# Pin

Top/Bottom Block protection

- Minimum 100,000 Program/Erase Cycles

- Allows XIP(execute in place)operation<sup>(1)</sup>

- Data retention

- -20-year data retention typical

- Fast Program/Erase Speed

-Page Program time: 0.6ms typical

-Sector Erase time: 50ms typical

-Block Erase time: 0.15/0.20 typical

-Chip Erase time: 25s typical

- Flexible Architecture

-Uniform Sector of 4K-byte

-Uniform Block of 32/64K-byte

- Low Power Consumption

- -1µA typical deep power down current

- -1µA typical standby current

- Advanced Security Features<sup>(1)</sup>

-128-Bit Unique ID for each device

-3\*1024-Byte Security Registers With OTP Locks

-Discoverable parameters (SFDP) register

- Single Power Supply Voltage

Full voltage range:2.7~3.6V

- Package Information

SOP8 (208mil)

DIP8 (300mil)

WSON8 (6\*5mm)

WSON8 (8\*6mm)

TFBGA-24(6\*4 ball array)

SOP16 (300mil)

USON8 (4\*4mm)

#### Note:

- 1. Please contact GigaDevice for details.

- 2. Hardware RESET# PIN is offered on special order. Please contact GigaDevice for details.

## GD25Q64C

## 2. GENERAL DESCRIPTION

The GD25Q64C (64M-bit) Serial flash supports the standard Serial Peripheral Interface (SPI), and supports the Dual/Quad SPI: Serial Clock, Chip Select, Serial Data I/O0 (SI), I/O1 (SO), I/O2 (WP#), and I/O3 (HOLD#). The Dual I/O data is transferred with speed of 240Mbits/s and the Quad I/O & Quad output data is transferred with speed of 480Mbits/s.

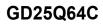

### **Connection Diagram**

#### **Pin Description**

| Pin Name I/O    |     | Description                               |  |  |

|-----------------|-----|-------------------------------------------|--|--|

| CS#             | I   | Chip Select Input                         |  |  |

| SO (IO1)        | I/O | Data Output (Data Input Output 1)         |  |  |

| WP# (IO2)       | I/O | Write Protect Input (Data Input Output 2) |  |  |

| VSS             |     | Ground                                    |  |  |

| SI (IO0)        | I/O | Data Input (Data Input Output 0)          |  |  |

| SCLK            | I   | Serial Clock Input                        |  |  |

| HOLD# (IO3) I/O |     | Hold Input (Data Input Output 3)          |  |  |

| VCC             |     | Power Supply                              |  |  |

Note: CS# must be driven high if chip is not selected. Please don't leave CS# floating any time after power is on.

GD25Q64C

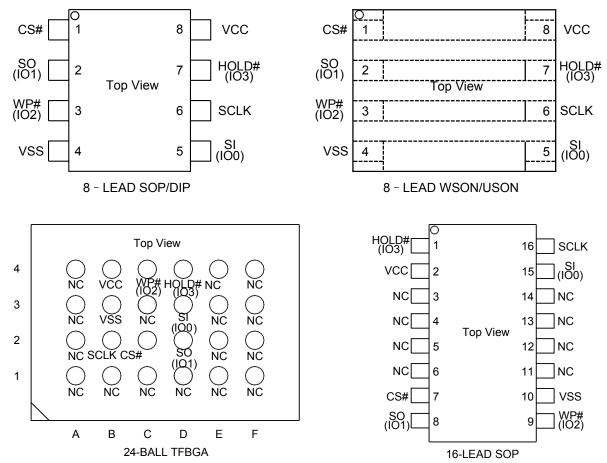

**Block Diagram**

# 3. MEMORY ORGANIZATION

## GD25Q64C

| Each device has | Each block has | Each sector has | Each page has |         |

|-----------------|----------------|-----------------|---------------|---------|

| 8M              | 64/32K         | 4K              | 256           | bytes   |

| 32K             | 256/128        | 16              | -             | pages   |

| 2048            | 16/8           | -               | -             | sectors |

| 128/256         | -              | -               | -             | blocks  |

## Uniform Block Sector Architecture GD25Q64C 64K Bytes Block Sector Architecture

| Block | Sector | Address range |         |  |

|-------|--------|---------------|---------|--|

|       | 2047   | 7FF000H       | 7FFFFH  |  |

| 127   |        |               |         |  |

|       | 2032   | 7F0000H       | 7F0FFFH |  |

|       | 2031   | 7EF000H       | 7EFFFH  |  |

| 126   |        |               |         |  |

|       | 2016   | 7E0000H       | 7E0FFFH |  |

|       |        |               |         |  |

|       |        |               |         |  |

|       |        |               |         |  |

|       |        |               |         |  |

|       |        |               |         |  |

|       |        |               |         |  |

|       | 47     | 02F000H       | 02FFFFH |  |

| 2     |        |               |         |  |

|       | 32     | 020000H       | 020FFFH |  |

|       | 31     | 01F000H       | 01FFFFH |  |

| 1     |        |               |         |  |

|       | 16     | 010000H       | 010FFFH |  |

|       | 15     | 00F000H       | 00FFFFH |  |

| 0     |        |               |         |  |

|       | 0      | 000000H       | 000FFFH |  |

## GD25Q64C

## 4. DEVICE OPERATION

### **SPI Mode**

#### Standard SPI

The GD25Q64C features a serial peripheral interface on 4 signals bus: Serial Clock (SCLK), Chip Select (CS#), Serial Data Input (SI) and Serial Data Output (SO). Both SPI bus mode 0 and 3 are supported. Input data is latched on the rising edge of SCLK and data shifts out on the falling edge of SCLK.

#### Dual SPI

The GD25Q64C supports Dual SPI operation when using the "Dual Output Fast Read" (3BH), "Dual I/O Fast Read" (BBH) and "Read Manufacture ID/ Device ID Dual I/O" (92H) commands. These commands allow data to be transferred to or from the device at twice the rate of the standard SPI. When using the Dual SPI command the SI and SO pins become bidirectional I/O pins: IO0 and IO1.

#### Quad SPI

The GD25Q64C supports Quad SPI operation when using the "Quad Output Fast Read" (6BH), "Quad I/O Fast Read"(EBH), "Quad I/O Word Fast Read" (E7H), "Read Manufacture ID/ Device ID Quad I/O" (94H) and "Quad Page Program" (32H) commands. These commands allow data to be transferred to or from the device at four times the rate of the standard SPI. When using the Quad SPI command the SI and SO pins become bidirectional I/O pins: IO0 and IO1, and WP# and HOLD# pins become IO2 and IO3. Quad SPI commands require the non-volatile Quad Enable bit (QE) in Status Register to be set.

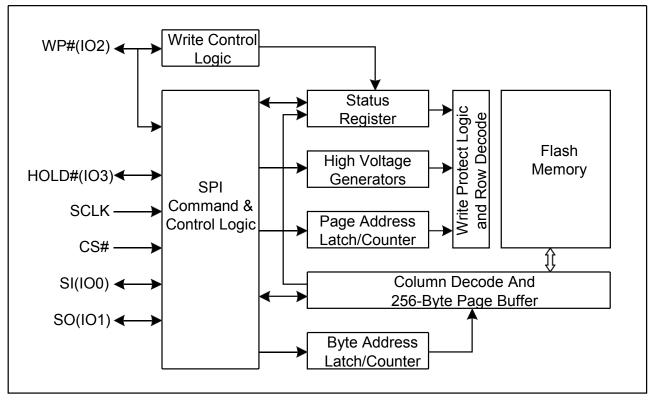

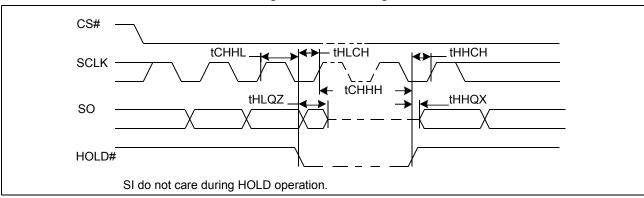

#### Hold

The HOLD# function is only available when QE=0, If QE=1, The HOLD# functions is disabled, the pin acts as dedicated data I/O pin.

The HOLD# signal goes low to stop any serial communications with the device, but doesn't stop the operation of write status register, programming, or erasing in progress.

The operation of HOLD, need CS# keep low, and starts on falling edge of the HOLD# signal, with SCLK signal being low (if SCLK is not being low, HOLD operation will not start until SCLK being low). The HOLD condition ends on rising edge of HOLD# signal with SCLK being low (If SCLK is not being low, HOLD operation will not end until SCLK beinglow).

The SO is high impedance, both SI and SCLK don't care during the HOLD operation, if CS# drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and then CS# must be at low.

Figure 1. Hold Condition

## GD25Q64C

## 5. DATA PROTECTION

The GD25Q64C provide the following data protection methods:

- Write Enable (WREN) command: The WREN command is set the Write Enable Latch bit (WEL). The WEL bit will

return to reset by the following situation:

- -Power-Up

-Write Disable (WRDI)

-Write Status Register (WRSR)

-Page Program (PP)

-Sector Erase (SE) / Block Erase (BE) / Chip Erase (CE)

-Software reset (66H+99H)

- Software Protection Mode: The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits define the section of the memory array that can be read but not change.

- ◆ Hardware Protection Mode: WP# goes low to protect the BP0~BP4 bits and SRP0~1 bits.

- Deep Power-Down Mode: In Deep Power-Down Mode, all commands are ignored except the Release from Deep Power-Down Mode command and reset command (66H+99H).

| ;   | Status F | Register | Conten | t   | Memory Content |                 |         |              |  |  |

|-----|----------|----------|--------|-----|----------------|-----------------|---------|--------------|--|--|

| BP4 | BP3      | BP2      | BP1    | BP0 | Blocks         | Addresses       | Density | Portion      |  |  |

| Х   | Х        | 0        | 0      | 0   | NONE           | NONE            | NONE    | NONE         |  |  |

| 0   | 0        | 0        | 0      | 1   | 126 to 127     | 7E0000H-7FFFFFH | 128KB   | Upper 1/64   |  |  |

| 0   | 0        | 0        | 1      | 0   | 124 to 127     | 7C0000H-7FFFFFH | 256KB   | Upper 1/32   |  |  |

| 0   | 0        | 0        | 1      | 1   | 120 to 127     | 780000H-7FFFFFH | 512KB   | Upper 1/16   |  |  |

| 0   | 0        | 1        | 0      | 0   | 112 to 127     | 700000H-7FFFFFH | 1MB     | Upper 1/8    |  |  |

| 0   | 0        | 1        | 0      | 1   | 96 to 127      | 600000H-7FFFFFH | 2MB     | Upper 1/4    |  |  |

| 0   | 0        | 1        | 1      | 0   | 64 to 127      | 400000H-7FFFFFH | 4MB     | Upper 1/2    |  |  |

| 0   | 1        | 0        | 0      | 1   | 0 to 1         | 000000H-01FFFFH | 128KB   | Lower 1/64   |  |  |

| 0   | 1        | 0        | 1      | 0   | 0 to 3         | 000000H-03FFFFH | 256KB   | Lower 1/32   |  |  |

| 0   | 1        | 0        | 1      | 1   | 0 to 7         | 000000H-07FFFFH | 512KB   | Lower 1/16   |  |  |

| 0   | 1        | 1        | 0      | 0   | 0 to 15        | 000000H-0FFFFH  | 1MB     | Lower 1/8    |  |  |

| 0   | 1        | 1        | 0      | 1   | 0 to 31        | 000000H-1FFFFFH | 2MB     | Lower 1/4    |  |  |

| 0   | 1        | 1        | 1      | 0   | 0 to 63        | 000000H-3FFFFFH | 4MB     | Lower 1/2    |  |  |

| Х   | Х        | 1        | 1      | 1   | 0 to 127       | 000000H-7FFFFH  | 8MB     | ALL          |  |  |

| 1   | 0        | 0        | 0      | 1   | 127            | 7FF000H-7FFFFFH | 4KB     | Top Block    |  |  |

| 1   | 0        | 0        | 1      | 0   | 127            | 7FE000H-7FFFFFH | 8KB     | Top Block    |  |  |

| 1   | 0        | 0        | 1      | 1   | 127            | 7FC000H-7FFFFFH | 16KB    | Top Block    |  |  |

| 1   | 0        | 1        | 0      | Х   | 127            | 7F8000H-7FFFFFH | 32KB    | Top Block    |  |  |

| 1   | 0        | 1        | 1      | 0   | 127            | 7F8000H-7FFFFFH | 32KB    | Top Block    |  |  |

| 1   | 1        | 0        | 0      | 1   | 0              | 000000H-000FFFH | 4KB     | Bottom Block |  |  |

| 1   | 1        | 0        | 1      | 0   | 0              | 000000H-001FFFH | 8KB     | Bottom Block |  |  |

| 1   | 1        | 0        | 1      | 1   | 0              | 000000H-003FFFH | 16KB    | Bottom Block |  |  |

| 1   | 1        | 1        | 0      | Х   | 0              | 000000H-007FFFH | 32KB    | Bottom Block |  |  |

Table1.0 GD25Q64C Protected area size (CMP=0)

宇翔达

Dual and Quad Serial Flash

GD25Q64C

1

1

1

0

0

000000H-007FFFH

32KB

Bottom Block

|     | Table1.1 GD25Q64C Protected area size (CMP=1) |          |        |                  |           |                 |        |             |  |  |  |  |

|-----|-----------------------------------------------|----------|--------|------------------|-----------|-----------------|--------|-------------|--|--|--|--|

|     | Status F                                      | Register | Conten | ıt               |           | Memory Content  |        |             |  |  |  |  |

| BP4 | 3P4 BP3 BP2 BP1 BP0                           |          | Blocks | Blocks Addresses |           | Portion         |        |             |  |  |  |  |

| Х   | X                                             | 0        | 0      | 0                | ALL       | 000000H-7FFFFFH | ALL    | ALL         |  |  |  |  |

| 0   | 0                                             | 0        | 0      | 1                | 0 to 125  | 000000H-7DFFFFH | 8064KB | Lower 63/64 |  |  |  |  |

| 0   | 0                                             | 0        | 1      | 0                | 0 to 123  | 000000H-7BFFFFH | 7936KB | Lower 31/32 |  |  |  |  |

| 0   | 0                                             | 0        | 1      | 1                | 0 to 119  | 000000H-77FFFFH | 7680KB | Lower 15/16 |  |  |  |  |

| 0   | 0                                             | 1        | 0      | 0                | 0 to 111  | 000000H-6FFFFH  | 7MB    | Lower 7/8   |  |  |  |  |

| 0   | 0                                             | 1        | 0      | 1                | 0 to 95   | 000000H-5FFFFFH | 6MB    | Lower 3/4   |  |  |  |  |

| 0   | 0                                             | 1        | 1      | 0                | 0 to 63   | 000000H-3FFFFFH | 4MB    | Lower 1/2   |  |  |  |  |

| 0   | 1                                             | 0        | 0      | 1                | 2 to 127  | 020000H-7FFFFFH | 8064KB | Upper 63/64 |  |  |  |  |

| 0   | 1                                             | 0        | 1      | 0                | 4 to 127  | 040000H-7FFFFFH | 7936KB | Upper 31/32 |  |  |  |  |

| 0   | 1                                             | 0        | 1      | 1                | 8 to 127  | 080000H-7FFFFFH | 7680KB | Upper 15/16 |  |  |  |  |

| 0   | 1                                             | 1        | 0      | 0                | 16 to 127 | 100000H-7FFFFFH | 7MB    | Upper 7/8   |  |  |  |  |

| 0   | 1                                             | 1        | 0      | 1                | 32 to 127 | 200000H-7FFFFFH | 6MB    | Upper 3/4   |  |  |  |  |

| 0   | 1                                             | 1        | 1      | 0                | 64 to 127 | 400000H-7FFFFFH | 4MB    | Upper 1/2   |  |  |  |  |

| Х   | Х                                             | 1        | 1      | 1                | NONE      | NONE            | NONE   | NONE        |  |  |  |  |

| 1   | 0                                             | 0        | 0      | 1                | 0 to 127  | 000000H-7FEFFFH | 8188KB | L-2047/2048 |  |  |  |  |

| 1   | 0                                             | 0        | 1      | 0                | 0 to 127  | 000000H-7FDFFFH | 8184KB | L-1023/1024 |  |  |  |  |

| 1   | 0                                             | 0        | 1      | 1                | 0 to 127  | 000000H-7FBFFFH | 8176KB | L-511/512   |  |  |  |  |

| 1   | 0                                             | 1        | 0      | х                | 0 to 127  | 000000H-7F7FFFH | 8160KB | L-255/256   |  |  |  |  |

| 1   | 0                                             | 1        | 1      | 0                | 0 to 127  | 000000H-7F7FFFH | 8160KB | L-255/256   |  |  |  |  |

| 1   | 1                                             | 0        | 0      | 1                | 0 to 127  | 001000H-7FFFFFH | 8188KB | U-2047/2048 |  |  |  |  |

| 1   | 1                                             | 0        | 1      | 0                | 0 to 127  | 002000H-7FFFFFH | 8184KB | U-1023/1024 |  |  |  |  |

| 1   | 1                                             | 0        | 1      | 1                | 0 to 127  | 004000H-7FFFFFH | 8176KB | U-511/512   |  |  |  |  |

| 1   | 1                                             | 1        | 0      | х                | 0 to 127  | 008000H-7FFFFH  | 8160KB | U-255/256   |  |  |  |  |

| 1   | 1                                             | 1        | 1      | 0                | 0 to 127  | 008000H-7FFFFFH | 8160KB | U-255/256   |  |  |  |  |

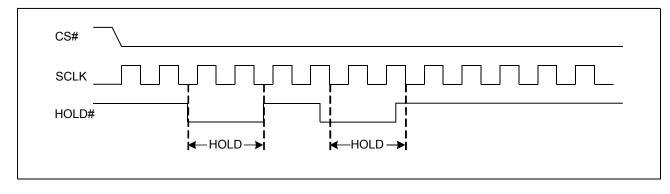

## 6. STATUS REGISTER

| S23      | S22  | S21  | S20 | S19      | S18      | S17        | S16      |

|----------|------|------|-----|----------|----------|------------|----------|

| Reserved | DRV1 | DRV0 | HPF | Reserved | Reserved | Reserved   | Reserved |

|          |      |      |     |          |          |            |          |

| S15      | S14  | S13  | S12 | S11      | S10      | <b>S</b> 9 | S8       |

| SUS1     | СМР  | LB3  | LB2 | LB1      | SUS2     | QE         | SRP1     |

|          |      |      |     |          |          |            |          |

| S7       | S6   | S5   | S4  | S3       | S2       | S1         | S0       |

| SRP0     | BP4  | BP3  | BP2 | BP1      | BP0      | WEL        | WIP      |

The status and control bits of the Status Register are as follows:

#### WIP bit.

The Write in Progress (WIP) bit indicates whether the memory is busy in program/erase/write status register progress. When WIP bit sets to 1, means the device is busy in program/erase/write status register progress, when WIP bit sets 0, means the device is not in program/erase/write status register progress.

#### WEL bit.

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write Status Register, Program or Erase command is accepted.

#### BP4, BP3, BP2, BP1, BP0 bits.

The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits are non-volatile. They define the size of the area to be software protected against Program and Erase commands. These bits are written with the Write Status Register (WRSR) command. When the Block Protect (BP4, BP3, BP2, BP1, BP0) bits are set to 1, the relevant memory area (as defined in Table1).becomes protected against Page Program (PP), Sector Erase (SE) and Block Erase (BE) commands. The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits can be written provided that the Hardware Protected mode has not been set. The Chip Erase (CE) command is executed, if the Block Protect (BP2, BP1, and BP0) bits are 0 and CMP=0 or the Block Protect (BP2, BP1, and BP0) bits are 1 and CMP=1.

#### SRP1, SRP0 bits.

The Status Register Protect (SRP1 and SRP0) bits are non-volatile Read/Write bits in the status register. The SRP bits control the method of write protection: software protection, hardware protection, power supply lock-down or one time programmable protection.

| SRP1 | SRP0                     | #WP                    | Status Register                       | Description                                                 |

|------|--------------------------|------------------------|---------------------------------------|-------------------------------------------------------------|

| 0    | 0 0 X Software Protected |                        | Software Protected                    | The Status Register can be written to after a Write Enable  |

| 0    | 0                        | ^                      | Soliware Protected                    | command, WEL=1.(Default)                                    |

| 0    | 1                        | 0                      | Hardware Protected                    | WP#=0, the Status Register locked and cannot be written to. |

| 0    |                          |                        | Hardwara Upprotected                  | WP#=1, the Status Register is unlocked and can be written   |

| 0    | 1                        | 1 Hardware Unprotected |                                       | to after a Write Enable command, WEL=1.                     |

| 1    | 0                        | х                      | Power Supply Lock-Down <sup>(1)</sup> | Status Register is protected and cannot be written to again |

| '    |                          |                        | (2)                                   | until the next Power-Down, Power-Up cycle.                  |

| 1    | 1                        | х                      | One Time Program <sup>(2)</sup>       | Status Register is permanently protected and cannot be      |

| '    |                          | ~                      |                                       | written to.                                                 |

NOTE:

1. When SRP1, SRP0= (1, 0), a Power-Down, Power-Up cycle will change SRP1, SRP0 to (0, 0) state.

GD25Q64C

2. This feature is available on special order (GD25Q64CxxSx). Please contact GigaDevice for details.

#### QE bit.

The Quad Enable (QE) bit is a non-volatile Read/Write bit in the Status Register that allows Quad operation. When the QE bit is set to 0 (Default) the WP# pin and HOLD# pin are enable. When the QE pin is set to 1, the Quad IO2 and IO3 pins are enabled. (It is best to set the QE bit to 0 to avoid short issue if the WP# or HOLD# pin is tied directly to the power supply or ground.)

#### LB3, LB2, LB1, bits.

The LB3, LB2, LB1, bits are non-volatile One Time Program (OTP) bits in Status Register (S13-S11) that provide the write protect control and status to the Security Registers. The default state of LB3-LB1 are 0, the security registers are unlocked. The LB3-LB1 bits can be set to 1 individually using the Write Register instruction. The LB3-LB1 bits are One Time Programmable, once they are set to 1, the Security Registers will become read-only permanently.

#### CMP bit

The CMP bit is a non-volatile Read/Write bit in the Status Register (S14). It is used in conjunction with the BP4-BP0 bits to provide more flexibility for the array protection. Please see the Status registers Memory Protection table for details. The default setting is CMP=0.

#### SUS1, SUS2 bit

The SUS1 and SUS2 bit are read only bits in the status register (S15 and S10) that are set to 1 after executing an Program/Erase Suspend (75H) command (The Erase Suspend will set the SUS1 to 1,and the Program Suspend will set the SUS2 to 1). The SUS1 and SUS2 bit are cleared to 0 by Program/Erase Resume (7AH) command, software reset (66H+99H) command as well as a power-down, power-up cycle.

#### HPF bit

The High Performance Flag (HPF) bit is read only bit, that indicates the status of High Performance Mode (HPM). When HPF bit is set to 1, it means the device is in High Performance Mode. When HPF bit is set to 0 (default), it means the device is not in High Performance Mode.

#### DRV1, DRV0 bits

The DRV1 & DRV0 bits are used to determine the output driver strength for the Read operations.

| DRV1, DRV0 | Driver Strength |

|------------|-----------------|

| 00         | 100%            |

| 01         | 75% (default)   |

| 10         | 50%             |

| 11         | 25%             |

## GD25Q64C

## 7. COMMANDS DESCRIPTION

All commands, addresses and data are shifted in and out of the device, beginning with the most significant bit on the first rising edge of SCLK after CS# is driven low. Then, the one-byte command code must be shifted in to the device, with most significant bit first on SI, and each bit is latched on the rising edges of SCLK.

See Table2, every command sequence starts with a one-byte command code. Depending on the command, this might be followed by address bytes, or by data bytes, or by both or none. CS# must be driven high after the last bit of the command sequence has been completed. For the commands of Read, Fast Read, Read Status Register or Release from Deep Power-Down, and Read Device ID, the shifted-in command sequence is followed by a data-out sequence. All read instruction can be completed after any bit of the data-out sequence is being shifted out, and then CS# must be driven high to return to deselected status.

For the commands of Page Program, Sector Erase, Block Erase, Chip Erase, Write Status Register, Write Enable, Write Disable or Deep Power-Down command, CS# must be driven high exactly at a byte boundary, otherwise the command is rejected, and is not executed. That means CS# must be driven high when the number of clock pulses after CS# being driven low is an exact multiple of eight. For Page Program, if CS# is driven high at any time the input byte is not a full byte, nothing will happen and WEL will not be reset.

| Command Name                              | Byte 1 | Byte 2                         | Byte 3                        | Byte 4                 | Byte 5         | Byte 6                 | n-Bytes      |

|-------------------------------------------|--------|--------------------------------|-------------------------------|------------------------|----------------|------------------------|--------------|

| Write Enable                              | 06H    |                                |                               |                        |                |                        |              |

| Write Disable                             | 04H    |                                |                               |                        |                |                        |              |

| Volatile SR                               | 50H    |                                |                               |                        |                |                        |              |

| Write Enable                              |        |                                |                               |                        |                |                        |              |

| Read Status Register-1                    | 05H    | (S7-S0)                        |                               |                        |                |                        | (continuous) |

| Read Status Register-2                    | 35H    | (S15-S8)                       |                               |                        |                |                        | (continuous) |

| Read Status Register-3                    | 15H    | (S23-S16)                      |                               |                        |                |                        | (continuous) |

| Write Status Register-1                   | 01H    | S7-S0                          |                               |                        |                |                        |              |

| Write Status Register-2                   | 31H    | S15-S8                         |                               |                        |                |                        |              |

| Write Status Register-3                   | 11H    | S23-S16                        |                               |                        |                |                        |              |

| Read Data                                 | 03H    | A23-A16                        | A15-A8                        | A7-A0                  | (D7-D0)        | (Next byte)            | (continuous) |

| Fast Read                                 | 0BH    | A23-A16                        | A15-A8                        | A7-A0                  | dummy          | (D7-D0)                | (continuous) |

| Dual Output<br>Fast Read                  | 3BH    | A23-A16                        | A15-A8                        | A7-A0                  | dummy          | (D7-D0) <sup>(1)</sup> | (continuous) |

| Dual I/O<br>Fast Read                     | BBH    | A23-A8 <sup>(2)</sup>          | A7-A0<br>M7-M0 <sup>(2)</sup> | (D7-D0) <sup>(1)</sup> | (Next<br>byte) | (Next byte)            | (continuous) |

| Quad Output<br>Fast Read                  | 6BH    | A23-A16                        | A15-A8                        | A7-A0                  | dummy          | (D7-D0) <sup>(3)</sup> | (continuous) |

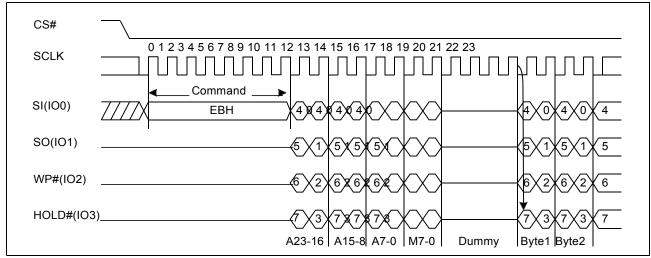

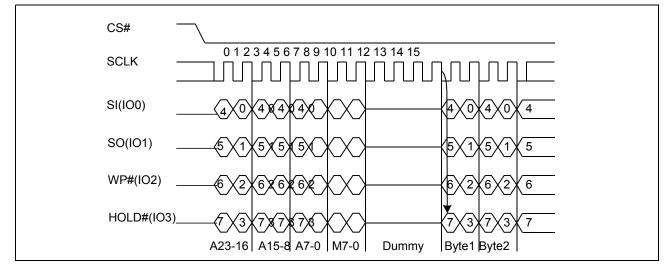

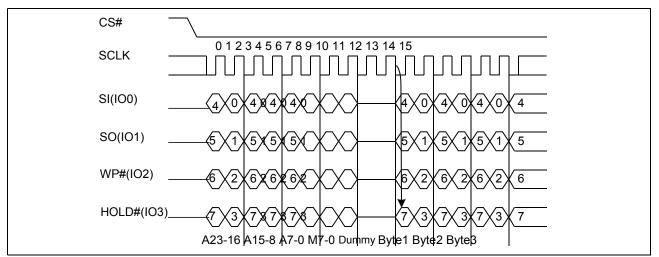

| Quad I/O<br>Fast Read                     | EBH    | A23-A0<br>M7-M0 <sup>(4)</sup> | dummy <sup>(5)</sup>          | (D7-D0) <sup>(3)</sup> | (Next<br>byte) | (Next byte)            | (continuous) |

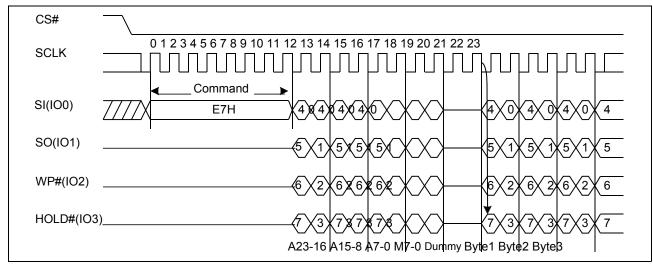

| Quad I/O Word<br>Fast Read <sup>(7)</sup> | E7H    | A23-A0<br>M7-M0 <sup>(4)</sup> | dummy <sup>(6)</sup>          | (D7-D0) <sup>(3)</sup> | (Next<br>byte) | (Next byte)            | (continuous) |

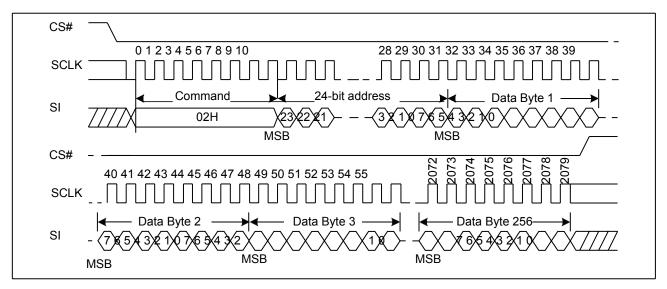

| Page Program                              | 02H    | A23-A16                        | A15-A8                        | A7-A0                  | D7-D0          | Next byte              | continuous   |

| Quad Page Program                         | 32H    | A23-A16                        | A15-A8                        | A7-A0                  | D7-D0          | Next byte              | continuous   |

| Fast Page Program                         | F2H    | A23-A16                        | A15-A8                        | A7-A0                  | D7-D0          | Next byte              | continuous   |

| Sector Erase                              | 20H    | A23-A16                        | A15-A8                        | A7-A0                  |                |                        |              |

| Block Erase(32K)                          | 52H    | A23-A16                        | A15-A8                        | A7-A0                  |                |                        |              |

| Block Erase(64K)                          | D8H    | A23-A16                        | A15-A8                        | A7-A0                  |                |                        |              |

| Chip Erase                                | C7/60  |                                |                               |                        |                |                        |              |

|                                           | Н      |                                |                               |                        |                |                        |              |

| Enable Reset                              | 66H    |                                |                               |                        |                |                        |              |

Table2. Commands (Standard/Dual/Quad SPI)

GD25Q64C

| 99H |                                                                                                                                                                 |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

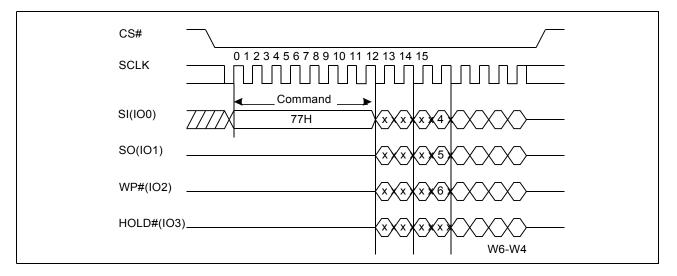

| 77H | dummy <sup>(9)</sup><br>W7-W0                                                                                                                                   |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 75H |                                                                                                                                                                 |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7AH |                                                                                                                                                                 |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ABH | dummy                                                                                                                                                           | dummy                                                       | dummy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (DID7-<br>DID0)                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                | (continuous)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ABH |                                                                                                                                                                 |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

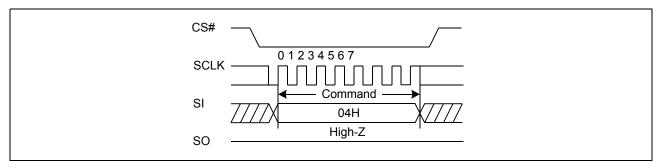

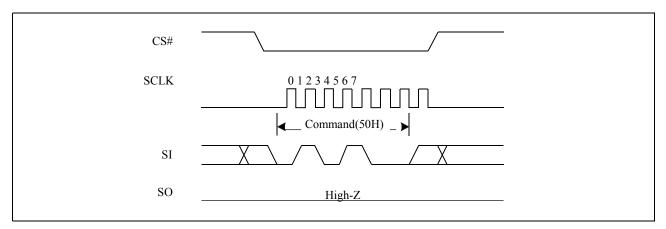

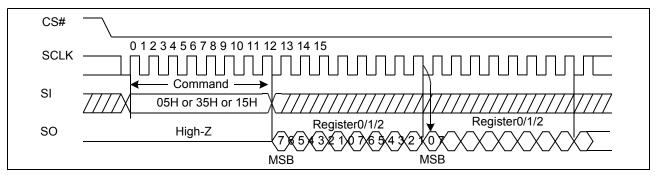

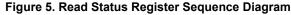

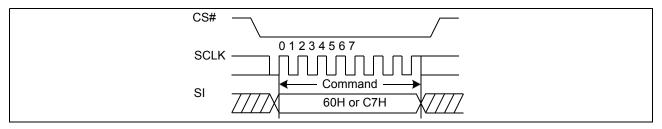

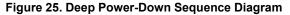

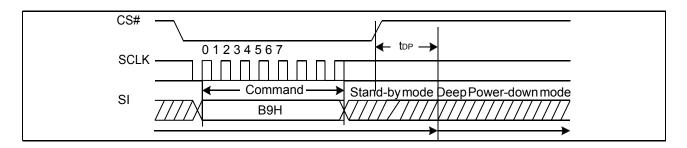

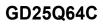

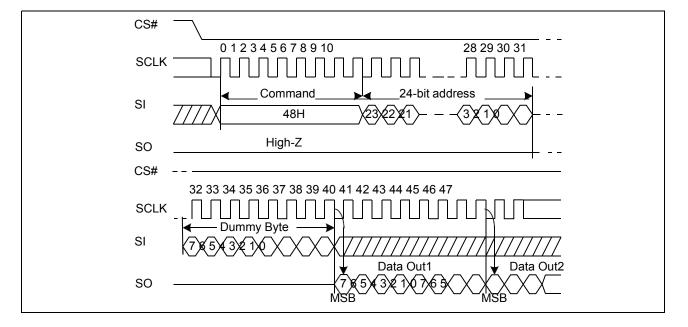

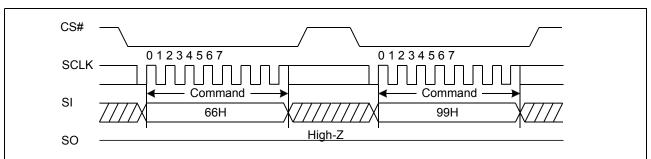

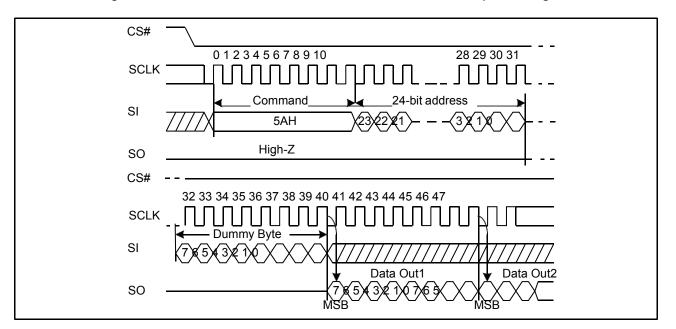

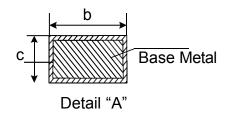

| B9H |                                                                                                                                                                 |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |