The Future of Analog IC Technology

# DESCRIPTION

The MP4012 is a current mode controller designed for driving the high brightness Light Emitting Diodes (LEDs) from extremely wide input voltage 8V~55V. It can be used in Boost, Buck, Buck-boost and SEPIC topologies.

The MP4012 drives external MOSFET with fixed frequency/constant off-time architecture to regulate the LED current, which is measured through an external current sense resistor. Its feedback voltage can be adjusted by the external DC bias voltage.

The MP4012 can work in constant frequency operation mode or constant off time mode. It features programmable slop compensation that can optimize the control loop regulation and avoid sub harmonic oscillation.

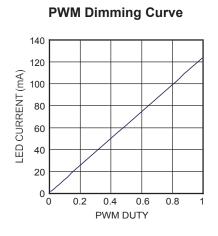

The MP4012 implements high frequency PWM Dimming with external disconnect MOSFET. It achieves analog dimming by adjusting the feedback voltage.

The MP4012 has synchronizing function, which makes multiple ICs synchronized to each other by connecting SYNC pins together.

The MP4012 includes under-voltage lockout, over voltage protection, open and short hiccup mode protection, overload protection and thermal protection to prevent damage in the case of fault condition.

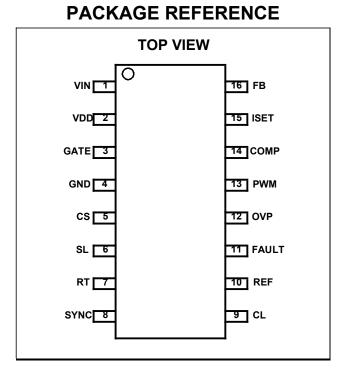

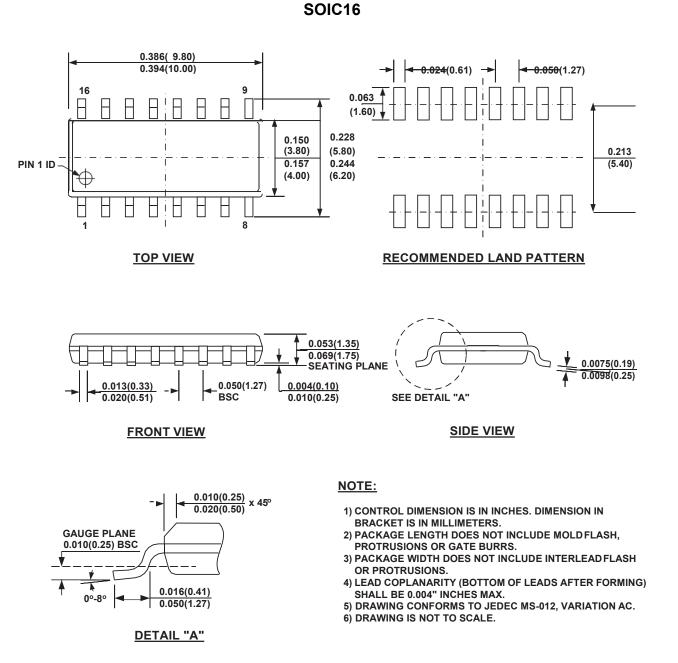

The MP4012 is available in a 16-pin SOIC package.

## **FEATURES**

- Constant-current WLED Controller

- 8V~55V Input Voltage

- Constant Frequency Mode Or Constant Off Time Mode

- Programmable Switching Frequency or Off-Time

- Leading Edge Blanking for Current Sense

- High Frequency PWM Dimming and Analog

Dimming

- Output-to-Input Disconnect in Shutdown

Mode

- Synchronization Function

- Programmable Over Voltage Protection

- Open Load Hiccup Mode Protection

- Short Load Hiccup Mode Protection

- Programmable Current Limit

- UVLO, Thermal Shutdown

- Soft Start

- Available in 16-pin SOIC package

## APPLICATIONS

- LCD Backlighting Applications

- DC/DC LED Controller Applications

- General Illumination

- Industrial Lighting

- Automotive/ Decorative LED Lighting

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

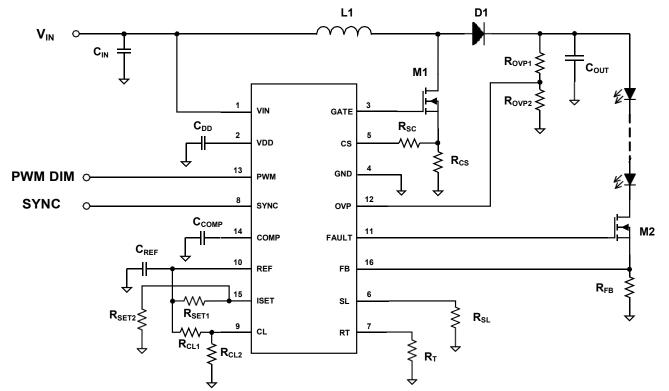

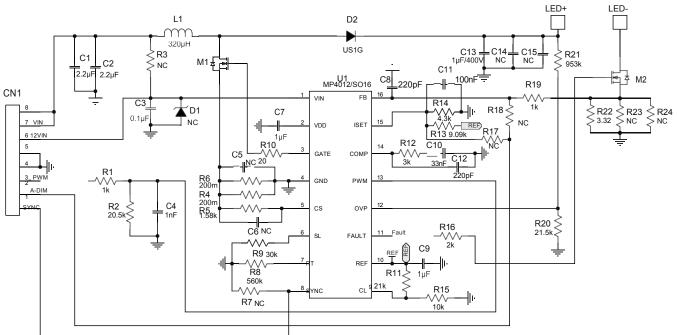

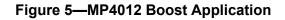

# **TYPICAL APPLICATION**

### **ORDERING INFORMATION**

| Part Number* | Package | Package Top Marking Free Air Temperatur |                |

|--------------|---------|-----------------------------------------|----------------|

| MP4012DS     | SOIC16  | MP4012                                  | -40°C to +85°C |

\*For Tape & Reel, add suffix –Z (e.g. MP4012DS–Z); For RoHS, compliant packaging, add suffix –LF (e.g. MP4012DS–LF–Z).

### ABSOLUTE MAXIMUM RATINGS (1)

| VIN                             | V to 60V                             |

|---------------------------------|--------------------------------------|

| VDD                             | V to 13.5V                           |

| VGATE, VFAULT, VPWM, VRT        | V to VDD+0.3V                        |

| All Other Pins                  | V to 6.5V                            |

| Junction Temperature            | 150°C                                |

| Lead Temperature                | 260°C                                |

| Continuous Power Dissipation (T | <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                 | 1.6 W                                |

### **Recommended Operating Conditions** <sup>(3)</sup>

| IN Supply Voltage VIN                        | V to 55V     |

|----------------------------------------------|--------------|

| Operating Junction Temp. (T <sub>J</sub> )40 | °C to +125°C |

# Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

SOIC16 ...... 80 ..... 30... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

### $V_{IN}$ =24V, $T_A$ = +25°C, unless otherwise noted.

| Parameters                           | Symbol               | Condition                                                                  | Min   | Тур   | Max   | Units |

|--------------------------------------|----------------------|----------------------------------------------------------------------------|-------|-------|-------|-------|

| Operating Input Voltage              | V <sub>IN</sub>      |                                                                            | 8     |       | 55    | V     |

| VDD Voltage                          | V <sub>VDD</sub>     | $V_{IN} \ge 8V$                                                            | 7.25  | 7.75  | 8.15  | V     |

| Supply Current (Shutdown)            | I <sub>SD</sub>      | V <sub>PWM</sub> = 0V                                                      |       | 0.8   | 1.0   | mA    |

| VDD Under Voltage Lockout            | UVLO                 | V <sub>DD</sub> Rising                                                     | 6.40  | 6.70  | 7.20  | V     |

| Under Voltage Lockout Hysteresis     |                      |                                                                            |       | 500   |       | mV    |

| VDD(external)                        |                      | Connect external DC voltage                                                |       |       | 12    | V     |

| Internal Regulator                   |                      |                                                                            |       |       |       |       |

| Reference Voltage                    | V <sub>REF</sub>     |                                                                            | 1.218 | 1.243 | 1.268 | V     |

| Reference Line Regulation            | V <sub>REFLINE</sub> | 0.1µF bypassed capacitor,<br>I <sub>REF</sub> =0 V <sub>DD</sub> =7.25-12V | 0     |       | 20    | mV    |

| Reference Load Regulation            | V <sub>REFLOAD</sub> | 0.1µF bypassed capacitor,<br>I <sub>REF</sub> =0-500uA                     | 0     |       | 13    | mV    |

| PWM Dimming                          |                      |                                                                            |       |       |       |       |

| PWM Low Threshold                    | V <sub>PWMI-LO</sub> | V <sub>PMWI</sub> Falling                                                  |       |       | 0.8   | V     |

| PWM High Threshold                   | V <sub>PWMI-HI</sub> | V <sub>PMWI</sub> Rising                                                   | 1.5   |       |       | V     |

| PWM Pull-down Resistance             | R <sub>PWM</sub>     |                                                                            | 50    | 100   | 150   | kΩ    |

| Gate                                 |                      |                                                                            |       |       |       |       |

| GATE Short Circuit Current           | I <sub>SOURCE</sub>  | V <sub>GATE</sub> =0V, V <sub>DD</sub> =7.75V                              | 0.2   | 0.4   |       | Α     |

| GATE Sink Current                    | I <sub>SINK</sub>    | V <sub>GATE</sub> =7.75V, V <sub>DD</sub> =7.75V                           | 0.4   | 0.7   |       | Α     |

| GATE Output Rise Time                | T <sub>RISE</sub>    | C <sub>GATE</sub> =1nF, V <sub>DD</sub> =7.75V                             |       | 50    | 85    | ns    |

| GATE Output Fall Time                | T <sub>FALL</sub>    | C <sub>GATE</sub> =1nF, V <sub>DD</sub> =7.75V                             |       | 25    | 45    | ns    |

| Current Sense                        |                      |                                                                            |       |       |       |       |

| Leading Edge Blanking                | T <sub>BLANK</sub>   |                                                                            | 100   |       | 250   | ns    |

| Delay to Output of COMP Comparator   | T <sub>DELAY1</sub>  |                                                                            |       |       | 200   | ns    |

| Delay to Output of CLIMIT Comparator | T <sub>DELAY2</sub>  |                                                                            |       |       | 200   | ns    |

| Comparator Offset Voltage            | V <sub>OFFSET</sub>  |                                                                            | -25   |       | 25    | mV    |

| Oscillator                           |                      |                                                                            |       |       | -     |       |

| Oscillator Frequency                 | f <sub>OSC1</sub>    | R <sub>T</sub> =96kΩ                                                       | 510   | 580   | 650   | kHz   |

| Oscillator Frequency                 | f <sub>OSC2</sub>    | R <sub>T</sub> =500kΩ                                                      | 100   | 115   | 130   | kHz   |

| Maximum Duty Cycle                   | D <sub>MAX</sub>     |                                                                            | 90    | 92    | 95    | %     |

| SYNC Input High                      | V <sub>SYNCH</sub>   |                                                                            | 1.5   |       |       | V     |

| SYNC Input Low                       | V <sub>SYNCL</sub>   |                                                                            |       |       | 0.8   | V     |

| SYNC Output Current                  | I <sub>SYNC</sub>    |                                                                            |       | 16    |       | μA    |

| Slope Compensation                   |                      |                                                                            |       |       |       |       |

| Current Source Out of SL Pin         | I <sub>SLOPE</sub>   |                                                                            | 0     |       | 95    | μA    |

| Internal Current Mirror Ratio        | G <sub>SLOPE</sub>   | $I_{SLOPE}$ =50μA, $R_{SL}$ =1kΩ                                           | 1.8   | 2.0   | 2.2   |       |

| Over Voltage Protection              |                      |                                                                            |       |       |       |       |

| OVP Threshold                        | V <sub>OVP-TH</sub>  |                                                                            | 4.60  | 4.95  | 5.30  | V     |

| OVP Threshold Hysteresis             |                      |                                                                            |       | 500   |       | mV    |

## ELECTRICAL CHARACTERISTICS (continued)

V<sub>IN</sub> =24V, T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameters                                                    | Symbol              | Condition                                                         | Min | Тур | Max | Units |

|---------------------------------------------------------------|---------------------|-------------------------------------------------------------------|-----|-----|-----|-------|

| Output Short Circuit Protection                               |                     |                                                                   |     |     |     |       |

| Gain for Short Circuit Comparator                             | G <sub>SC</sub>     |                                                                   | 1.8 | 2.0 | 2.2 |       |

| Propagation time for short circuit detection                  | T <sub>OFF</sub>    | I <sub>SET</sub> =200mV, FB=450mV,<br>FAULT goes form high to low |     |     | 250 | ns    |

| Fault Output Rise Time                                        | T <sub>RISE</sub>   | 330pF capacitor at FAULT pin                                      |     |     | 300 | ns    |

| Fault Output Fall Time                                        | T <sub>FALL</sub>   | 330pF capacitor at FAULT pin                                      |     |     | 200 | ns    |

| Short Circuit Detecting Blanking Time                         | T <sub>SC_BT</sub>  |                                                                   | 500 |     | 950 | ns    |

| Current Source/Sink at COMP Pin for<br>Hiccup Mode Protection | I <sub>HICCUP</sub> |                                                                   |     | 5.0 |     | μA    |

| Thermal Shutdown <sup>(5)</sup>                               |                     |                                                                   |     | 150 |     | °C    |

Notes:

5) Guaranteed by design

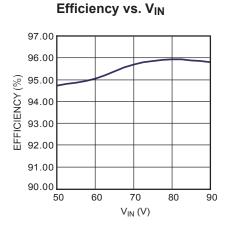

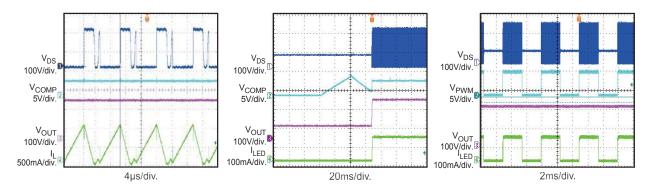

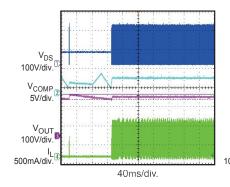

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Performance waveforms are tested on the evaluation board of Typical Application Circuit (Figure 5).

$V_{IN}$  = 64V, 12VIN=12V, I<sub>LED</sub> = 120mA, VLED=200V, 66WLEDs in series, T<sub>A</sub> = 25°C, Boost Application, unless otherwise noted.

**Steady State**

Soft Start

**PWM Dimming**

**OVP Recovery**

Short Load Recovery

# **PIN FUNCTIONS**

| Pin # | Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN   | Input Supply Pin. It is the input of internal linear regulator. Must be locally bypassed.                                                                                                                                                                                                                                                                                                                           |

| 2     | VDD   | The Internal Linear Regulator Output Pin. VDD provides power supply for the external MOSFET gate driver and the internal control circuitry. Bypass VDD to GND with a 0.47µF or larger ceramic capacitor.                                                                                                                                                                                                            |

| 3     | GATE  | External MOSFET Gate Driver Pin.                                                                                                                                                                                                                                                                                                                                                                                    |

| 4     | GND   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5     | CS    | Switch Current Sense Input Pin. It is used to sense the current of the external power FET. It has a built-in 100ns (min) blanking time.                                                                                                                                                                                                                                                                             |

| 6     | SL    | Slope Compensation Pin for current sense. Connecting a resistor between SL and GND programs the slope compensation. In case of constant off-time mode of operation, slope compensation is unnecessary and let this pin open.                                                                                                                                                                                        |

| 7     | RT    | Switching frequency/off-time set Pin. A resistor connected between this pin and GND/GATE sets the frequency/off-time.                                                                                                                                                                                                                                                                                               |

| 8     | SYNC  | Synchronization Pin. Connecting the multiple MP4012 SYNC pins together to achieve the synchronous working mode.                                                                                                                                                                                                                                                                                                     |

| 9     | CL    | Current Limit Set Pin. This pin sets the external MOSFET current limit. The current limit can be set by using a resistor divider from the REF pin to GND.                                                                                                                                                                                                                                                           |

| 10    | REF   | Reference Output Pin. A $0.1\mu$ F or larger ceramic capacitor should be connected to bypass this pin to GND.                                                                                                                                                                                                                                                                                                       |

| 11    | FAULT | Fault Indication Output Pin. This pin is pulled down to GND in case of short circuit condition or over voltage condition. It is also used to drive the external MOSFET to disconnect the load from Vin for boost converter.                                                                                                                                                                                         |

| 12    | OVP   | Over Voltage Protection Input Pin. Connect a resistor divider from output to this pin to program the OVP threshold. When the voltage of this pin reaches 4.95V, the MP4012 triggers over voltage protection.                                                                                                                                                                                                        |

| 13    | PWM   | PWM Dimming Input Pin. Apply a PWM signal on this pin for brightness control. The GATE is disabled when PWM signal is low. The GATE is enabled when PWM signal is high.                                                                                                                                                                                                                                             |

| 14    | СОМР  | Converter Compensation Pin. This pin is used to compensate the regulation control loop. Connect a capacitor or a series RC network from COMP to GND. COMP pin is also used for hiccup timer. At IC start up, short protection or over voltage protection, the 5uA current source charges COMP pint until 5V, and then the 5µA current source discharges COMP voltage. IC is active when COMP voltage reduces to 1V. |

| 15    | ISET  | LED Current Set Pin. Connect a resistor divider from REF pin to set the LED current reference. The analog dimming function can be achieved through adjusting the voltage on ISET pin.                                                                                                                                                                                                                               |

| 16    | FB    | Feedback Input Pin. Connect a current sense resistor from FB to GND. The MP4012 regulates the voltage across the current sense resistor. The regulation voltage is set by ISET pin.                                                                                                                                                                                                                                 |

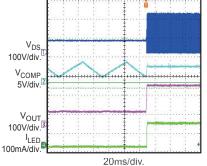

### **OPERATION**

The MP4012 drives external MOSFET with current mode architecture to regulate the LED current, which is measured through an external current sense resistor. Figure 1 shows the functional block diagram.

MP4012 employs a special circuit for regulating the internal power supply, which covers a wide input voltage from 8V to 55V. The 7.75V linear regulator provides all the power for internal circuits and external MOSFET gate drive energy. MP4012 has a 2% accurate 1.25V reference, which is used as the reference for LED current. The reference is also used to set the current limit and over voltage threshold.

MP4012 can be programmed as constant switching frequency (CF) or constant off time (CT) operation. Connecting a resistor between RT pin and GND sets the switching frequency for CF mode. Connecting a resistor between RT pin and GATE pin sets the off time for CT mode. For constant switching frequency mode, MP4012 includes a slope compensation section to ensure the converter stability when duty cycle is greater than 0.5.

For synchronization, the SYNC pins of multiple MP4012 can be connected together, and may also be connected to the open drain output of a master clock. When connected in this manner, the oscillators will lock to the device with the highest operating frequency.

MP4012 has two high-speed current comparators. One is used during normal operation, which contains an internal 100ns blanking time to prevent the current spike from mis-triggering the comparator. The other is used to limit the maximum switch current, which is programmable by connecting a resistor divider from REF pin.

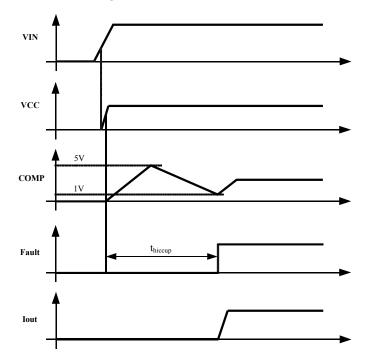

### Start up

The start up process is shown in Figure 2. During start up, the COMP is charged to 5V first, then it is discharged by an internal current source, MP4012 is active until the COMP voltage is discharged to 1V. The high level Fault turns on the external disconnected MOSFET. The output current is regulated by the converter.

Figure 2—Start up Process

### **Analog Dimming**

Analog dimming can be accomplished by varying the voltage at the ISET pin. This can be done either by using resistor divider from the REF pin or by applying an external DC voltage at the ISET pin.

### **PWM Dimming**

PWM dimming can be achieved by applying a square wave signal on PWM pin. The PWM signal controls the internal error amplifier (EA), FAULT output and GATE output. When the PWM signal is high, the GATE and FAULT pins are enabled, and the output of the EA is connected to the external compensation network. So the LED current is regulated accurately. When the PWM signal goes low, the GATE signal is disable. And the FAULT pin is pulled down to GND to turn off the disconnecting MOSFET. Meanwhile the output of the EA is disconnected from the compensation network. Thus, the COMP voltage

can be hold by external capacitor. And the disconnecting MOSFET can prevent the output voltage from being discharged, which helps to achieve the high frequency PWM dimming with better linear dimming performance.

#### Protection

MP4012 includes short circuit protection and over voltage protection, If the fault conditions are detected (either short circuit or open circuit), the COMP pin is disconnected from the internal EA and the Gate and Fault pins are pulled down to disable the LED controller, once the fault is remove, the COMP pin is charged by an internal current source until it reaches 5V, then the COMP is discharged by an internal current source. When it reaches 1V, the current source is disconnected from COMP pin and the internal EA is connected to it, the Fault pin starts to go high and the Gate pin is allowed to switch.

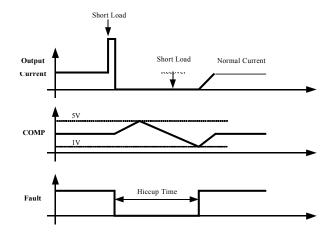

The short circuit threshold current is internally set to 200% of the steady state current. When the output current becomes higher than the short circuit threshold after some delay, the short circuit protection circuit is activated. See Figure 3. This allows the LED drive system auto-restart in an accident short condition without having to reset the IC.

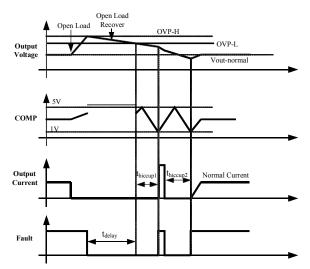

The open load protection is achieved through detecting the OVP pin voltage. When open load fault occurs, the output voltage rises as the output capacitor is still charged. The over voltage protection turns off the MP4012 and takes FAULT to GND when the OVP pin exceeds 4.95V. The converter turns on when the output voltage falls below the falling OVP threshold after a hiccup mode delay timer. MP4012 will repeat the process until the open load fault is removed.

When recovering from the open load condition, the output current might have some spike which caused by the high output voltage, and trigger the short load protection. But it can enter normal work mode when output voltage is close to the normal value. See Figure 4.

Figure 3 — Hiccup Mode Short Load Protection

Figure 4 — Open Load Protections

## **APPLICATION INFORMATION**

#### Switching Frequency Set

An external resistor  $R_T$  on RT pin can be used to set the switching frequency through the following equation:

$$\tau_{s} = \frac{55.6 \times 10^{\circ}}{R_{T}}$$

#### **LED Current Set**

Choose an external current sense resistor (R<sub>FB</sub>) to set the LED current.

$$R_{FB} = \frac{V_{ISET}}{I_{LED}}$$

Here,  $V_{ISET}$  is LED current reference on ISET pin, which is set by a resistor divider from REF pin to GND. It is recommended to add a 0.1uF ceramic capacitor on ISET pin to avoid noise injection.

#### **Over Voltage Protection Set**

Choose a voltage divider ( $R_{OVP1}$ ,  $R_{OVP2}$  in typical application) from the output to set the over voltage protection threshold:

$$V_{OVP} = 4.95V \times \frac{R + R}{R_{OVP2}}$$

#### **Slope Compensation**

MP4012 employs peak current mode control which need slope compensation to avoid subharmonic oscillation when duty cycle exceeds 50%. To ensure current loop stability, choosing a slope compensation which is at least half of the down slope of inductor current.

The slope compensation is set by two external resistors  $R_{SL}$  and  $R_{SC}$ . The slope compensation resistor can be calculated as:

$$R_{SC} = R_{SL} \times R_{CS} \times S_{DOWN} \times T_{S} \times 10^{5}$$

$S_{\text{DOWN}}$  (A/µs) is the down slope of the inductor current.

$$S_{\text{DOWN}} = \frac{V_{\text{L}}}{L}$$

Where  $V_L$  is the voltage across the inductor, and L is the inductor value.

$T_s$  is the switching period, which is set by the frequency set resistor  $R_T$ .

$R_{CS}$  is the current sense resistor which senses the switch current. It is recommended that the current sense resistor  $R_{CS}$  can be chosen to provide 200mV current sense signal (also need to take the power consumption into consideration).

The R<sub>SL</sub> is the slope resistor on SL pin, its value is limited by the maximum source current of SL pin. The minimum value of R<sub>SL</sub> is  $25k\Omega$ .  $25k\Omega - 50k\Omega$  of slope resistor value is recommended.

### **Current Limit**

Current limit value can be set by a resistor divider from REF pin to GND. The voltage of CL can be set as:

$$V_{CL} \ge 1.2 \times I_{PK} \times R_{CS} + \frac{4.5 \times R_{SC}}{R_{SL}}$$

Here, I<sub>PK</sub> is peak current of inductor.

The  $V_{CL}$  value should NOT be greater than 450mV, NO capacitor should be connected between CL pin and GND.

### **Hiccup Timer**

If the fault conditions are detected (either short circuit or open circuit), the COMP pin is disconnected from the internal EA and the Gate and Fault pins are pulled down to disable the LED controller. Once the fault condition is cleared, the COMP pin is charged by an internal 5 $\mu$ A current source until it reaches 5V, then the COMP is discharged by an internal 5 $\mu$ A current source. When it reaches 1V, the current source is disconnected from COMP pin and the internal EA is reconnected to it, the Fault pin starts to go high and the Gate pin is allowed to switch. The hiccup timer can be programmed by R -C network (R<sub>z</sub>, C<sub>z</sub> in series and parallel with C<sub>c</sub>) on COMP pin.

The delay time of Startup (Figure 2) can be approximately calculated as:

$$\mathsf{t}_{\mathsf{hiccup}\,\approx}\,(C_{C}+\,C_{Z})\frac{9\mathsf{V}}{5\mu\mathsf{A}}$$

In most case the voltage drop on  $R_Z$  can be neglected.

The hiccup time of Over Current Protection (Figure 3) can be approximately calculated as:

$$t_{\text{hiccup}} \approx \left(C_c + C_z\right) \frac{9V\text{-}V_{\text{COMP}}}{5\mu A}$$

Here,  $V_{\text{COMP}}$  is the voltage of COMP when fault condition is detected.

The hiccup time of Over Voltage Protection (Figure 4) can be approximately calculated as:

$$\begin{split} t_{delay} &\approx 0.1 \times \left(R_{OVP1} + R_{OVP2}\right) \times C_{O} \\ t_{hiccup1} &\approx \left(C_{C} + C_{Z}\right) \frac{9V - V_{COMP}}{5\mu A} \\ t_{hiccup2} &\approx \left(C_{C} + C_{Z}\right) \frac{8V}{5\mu A} \end{split}$$

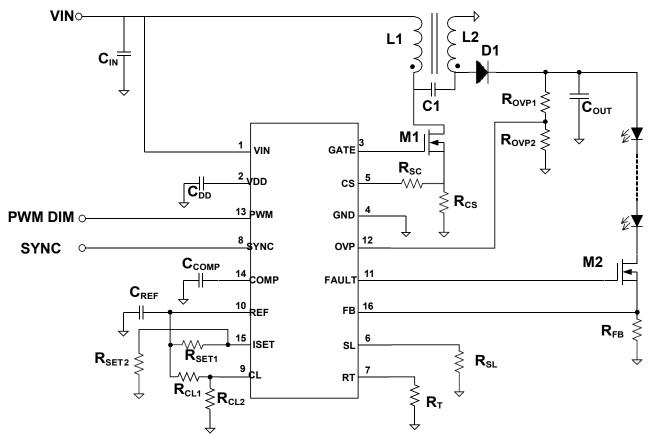

# **TYPICAL APPLIACTION CIRCUIT**

Figure 6—Typical Application Circuit for TV LED Backlighting

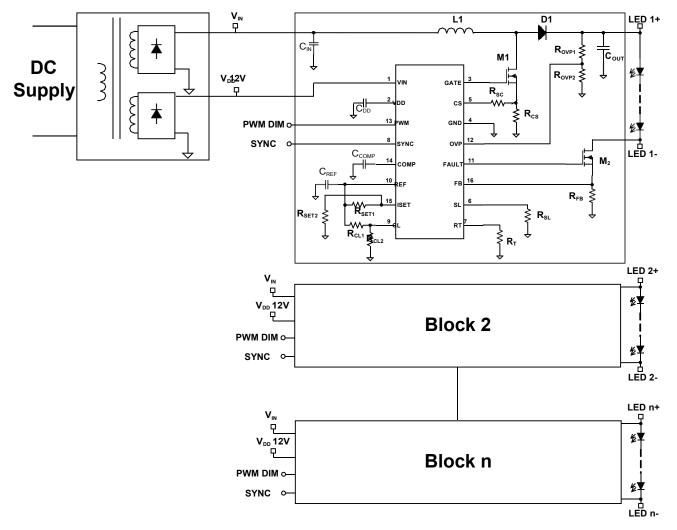

Figure 7—MP4012 Sepic Application Circuit

# PACKAGE INFORMATION

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.